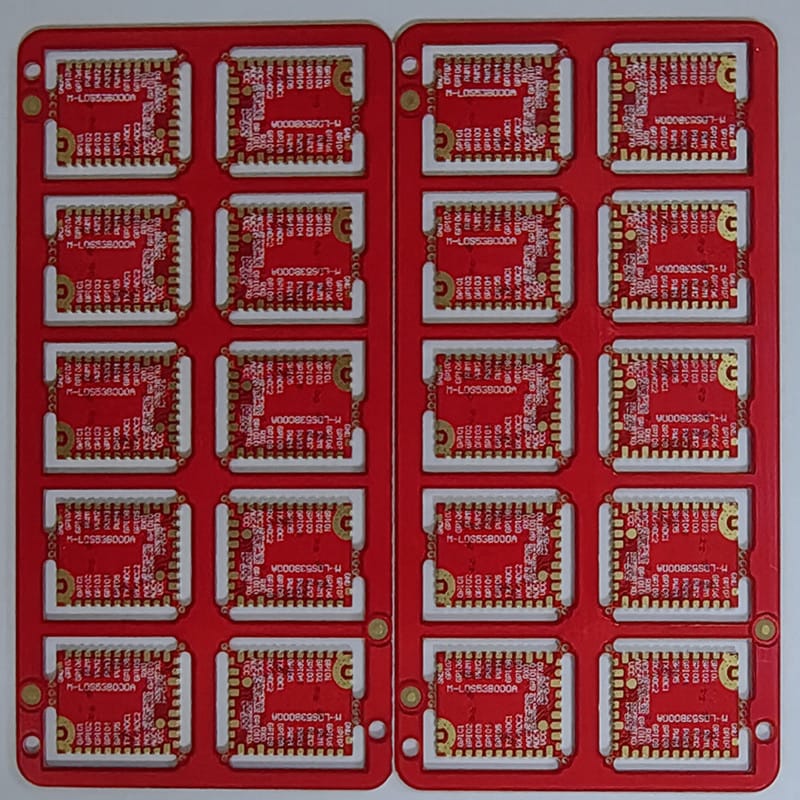

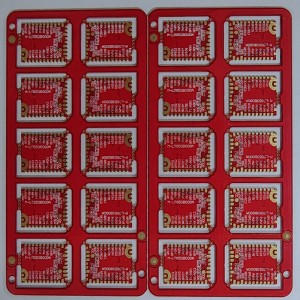

Prototype printplaten ROOD soldeermasker gekanteelde gaten

Productspecificatie:

| Basismateriaal: | FR4 TG140 |

| PCB-dikte: | 1,0+/-10% mm |

| Aantal lagen: | 4L |

| Koperdikte: | 1/1/1/1 oz |

| Oppervlaktebehandeling: | ENIG 2U” |

| Soldeermasker: | Glanzend rood |

| Zeefdruk: | Wit |

| Speciaal proces: | Pth halve gaten aan de randen |

Sollicitatie

De processen van geplateerde halve gaten zijn:

1. Bewerk het halve zijgat met het dubbele V-vormige snijgereedschap.

2. De tweede boor voegt geleidingsgaten toe aan de zijkant van het gat, verwijdert vooraf de koperen huid, vermindert bramen en gebruikt groeffrezen in plaats van boren om de snelheid en valsnelheid te optimaliseren.

3. Dompel koper onder om het substraat te galvaniseren, zodat er een laagje koper galvaniseert op de wand van het ronde gat aan de rand van de plaat.

4. Productie van het buitenste laagcircuit na lamineren, belichten en ontwikkelen van het substraat in volgorde, wordt het substraat onderworpen aan secundaire koperplating en vertinking, zodat de koperlaag op de gatwand van het ronde gat aan de rand van de plaat wordt verdikt en de koperlaag wordt bedekt met bedekt met een tinlaag voor corrosiebestendigheid;

5. Vormen van een half gat Snijd het ronde gat aan de rand van het bord doormidden, zodat er een half gat ontstaat;

6. Tijdens de stap van het verwijderen van de film wordt de anti-galvaniseerfilm die tijdens het filmpersingsproces is aangedrukt, verwijderd;

7. Etsen Het substraat wordt geëtst en het blootliggende koper op de buitenste laag van het substraat wordt verwijderd door etsen;

8. Tinstrippen Het substraat wordt van tin ontdaan, zodat het tin op de halve gatwand kan worden verwijderd en de koperlaag op de halve gatwand wordt blootgelegd.

9. Plak na het vormen de printplaten aan elkaar met rode tape en verwijder de bramen via de alkalische etslijn.

10. Na de tweede koperplating en vertinking op het substraat, wordt het ronde gat aan de rand van de plaat doormidden gesneden om een half gat te vormen, omdat de koperlaag van de gatwand bedekt is met een tinlaag en de koperlaag van de gatwand volledig intact is met de koperlaag van de buitenste laag van het substraat. Verbinding, waarbij een sterke bindingskracht betrokken is, kan effectief voorkomen dat de koperlaag op de gatwand wordt losgetrokken of dat het koper kromtrekt bij het snijden;

11. Nadat het vormen van het halve gat is voltooid, wordt de film verwijderd en vervolgens geëtst, zodat het koperoppervlak niet wordt geoxideerd. Zo wordt effectief het ontstaan van restkoper of zelfs kortsluiting vermeden en wordt de opbrengst van de gemetalliseerde PCB-printplaat met half gat verbeterd.

Veelgestelde vragen

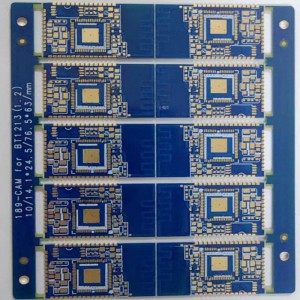

Een geplateerde halve-gat- of kanteelvormige-gat-rand is een stempelvormige rand die door de omtrek is doorgesneden. Een geplateerde halve-gat-rand is een hoger niveau van geplateerde randen voor printplaten, die meestal worden gebruikt voor board-to-board-verbindingen.

Via's worden gebruikt als verbinding tussen koperlagen op een printplaat, terwijl de PTH doorgaans groter is dan via's en dient als een geplateerd gat voor de aansluiting van componentkabels, zoals niet-SMT-weerstanden, condensatoren en DIP-behuizingen. PTH's kunnen ook worden gebruikt als gaten voor mechanische verbindingen, terwijl via's dat niet kunnen.

De plating op de doorlopende gaten is van koper, een geleider, waardoor elektrische geleiding door de printplaat mogelijk is. Niet-geplateerde doorlopende gaten hebben geen geleidbaarheid, dus als je ze gebruikt, kun je slechts aan één kant van de printplaat bruikbare koperen sporen hebben.

Er zijn 3 soorten gaten in een printplaat: Plated Through Hole (PTH), Non-Plated Through Hole (NPTH) en Via Holes. Deze moeten niet worden verward met sleuven of uitsparingen.

Volgens de IPC-standaard bedraagt deze +/-0,08 mm voor pth en +/-0,05 mm voor npth.